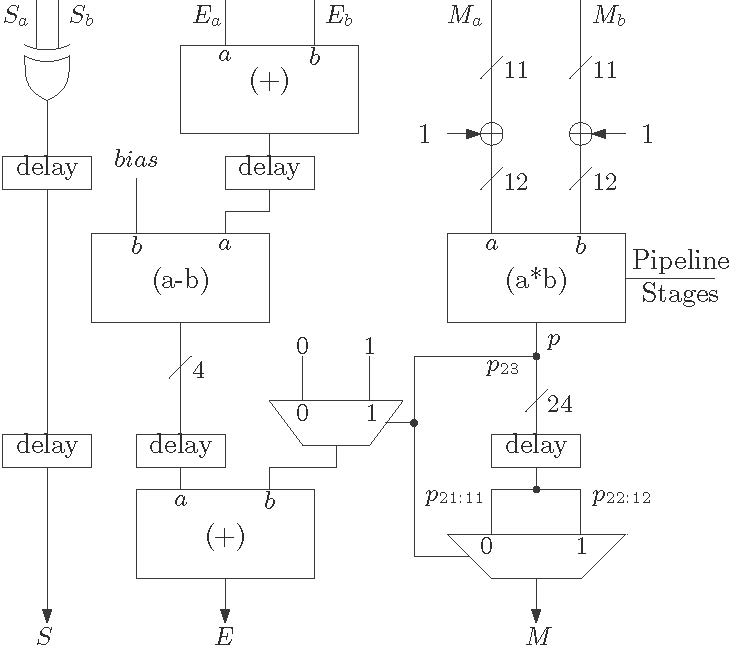

The algorithm flow chart of the 32-bit floating point multiplication... | Download Scientific Diagram

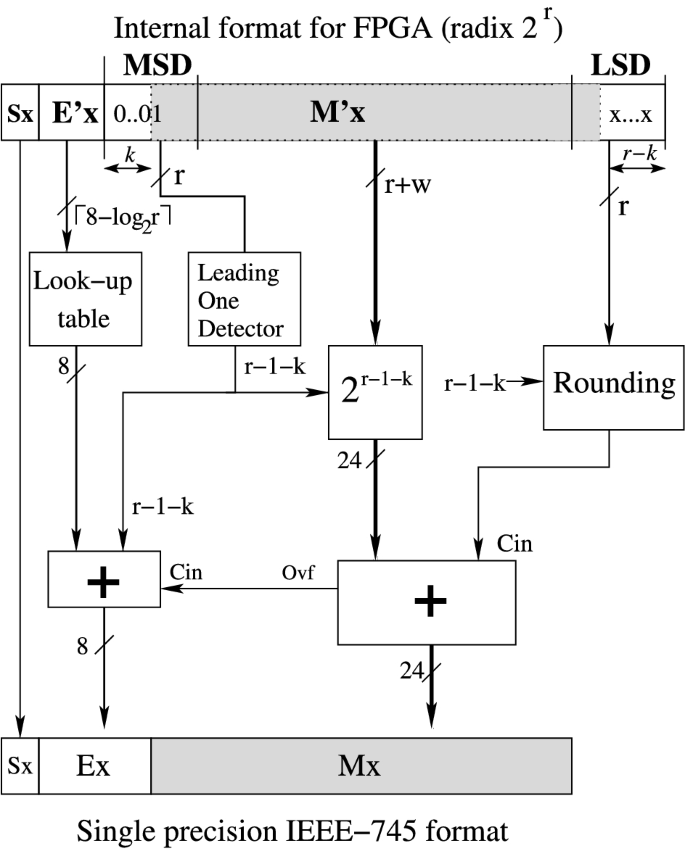

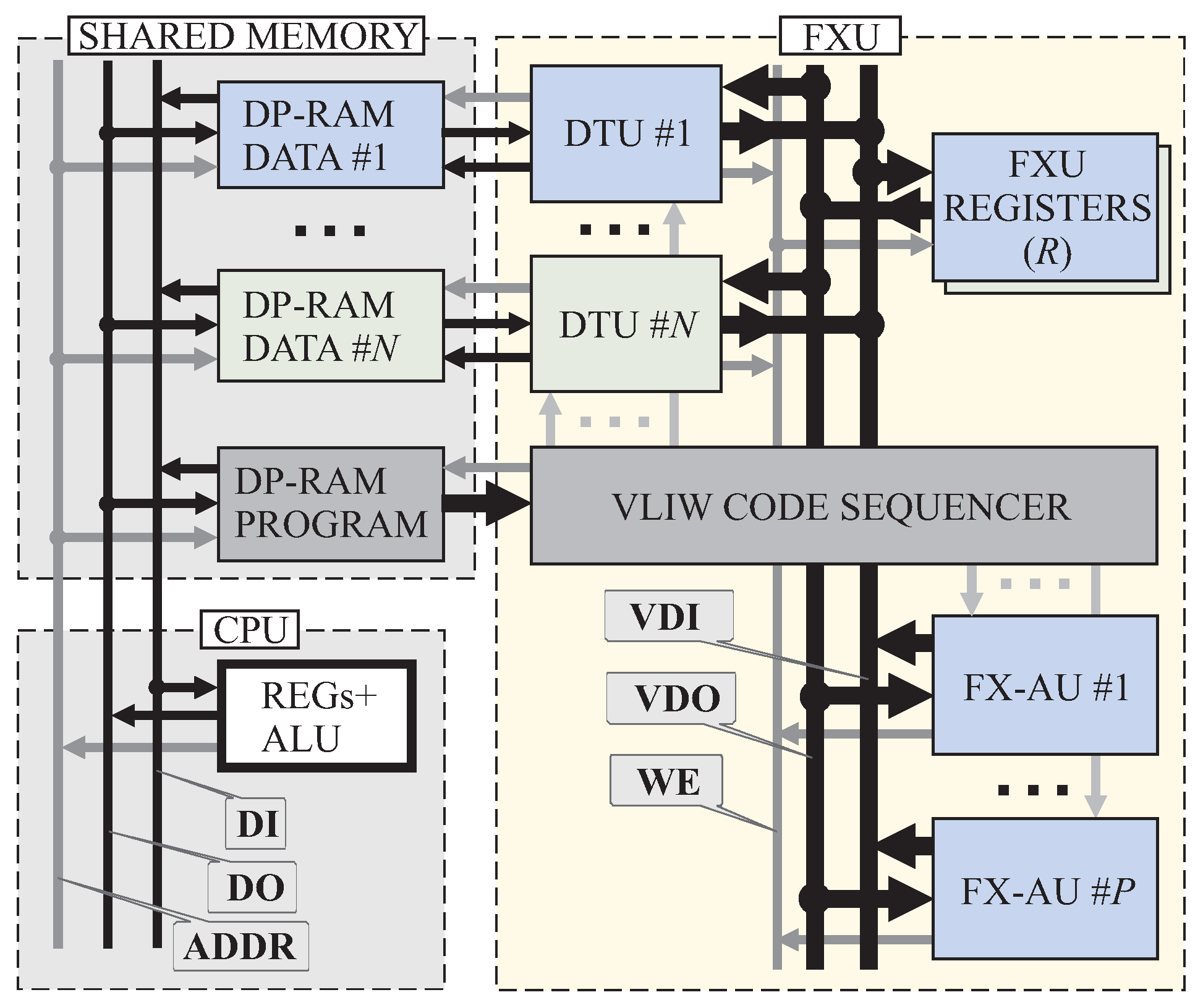

Electronics | Free Full-Text | Fixed-Point Arithmetic Unit with a Scaling Mechanism for FPGA-Based Embedded Systems | HTML

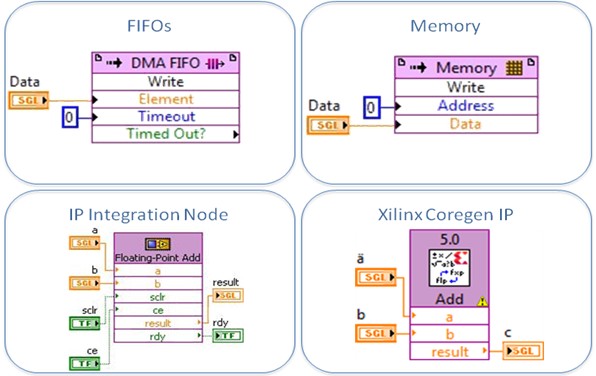

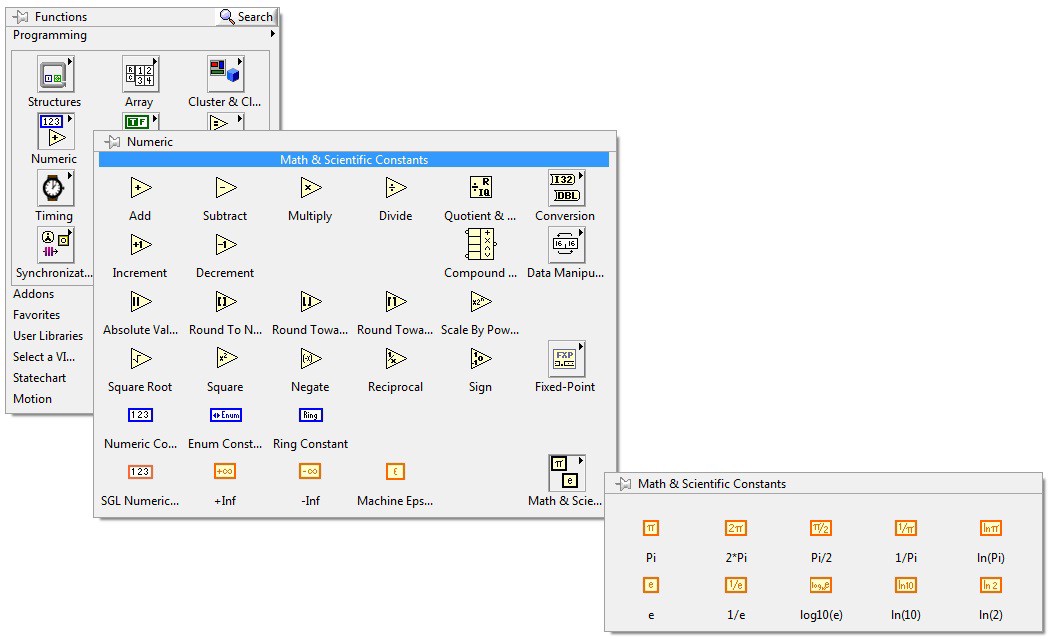

LogiCORE IP Floating-Point Operator v5 - Xilinx · PDF file† Available for Kintex™-7, Virtex ... Floating-Point core treats all NaNs as Quiet NaNs. When any NaN is supplied as

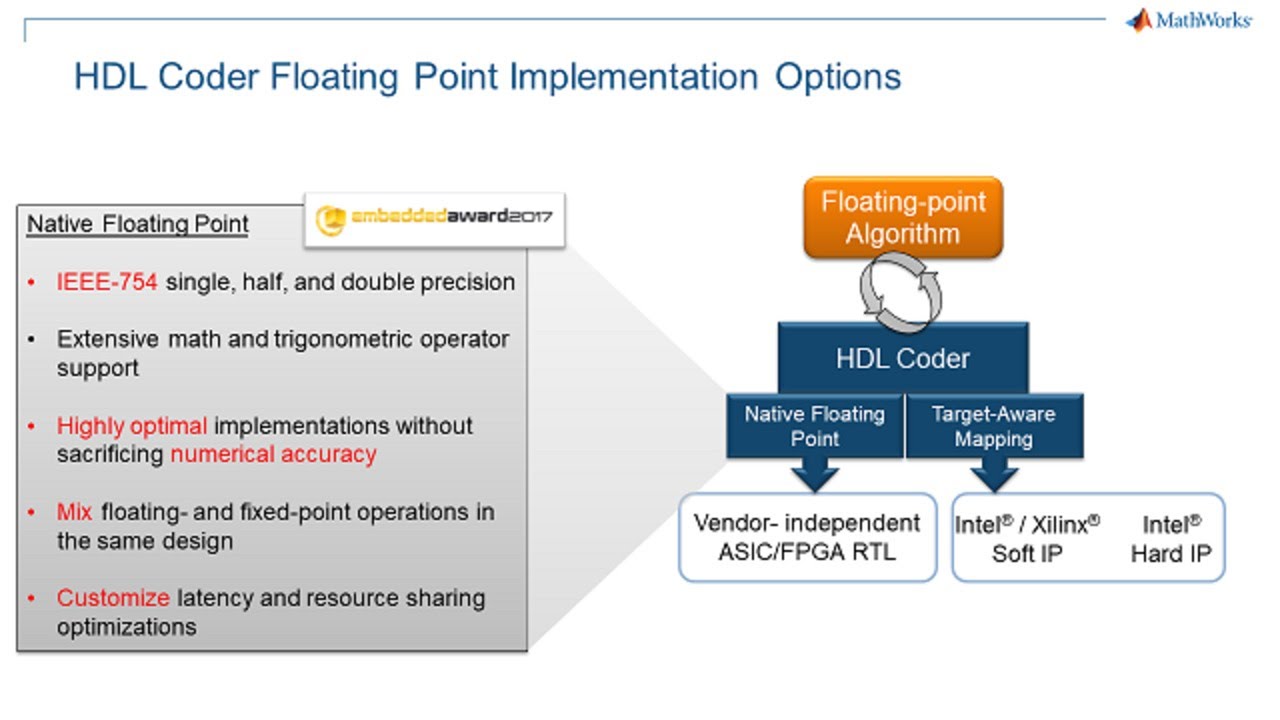

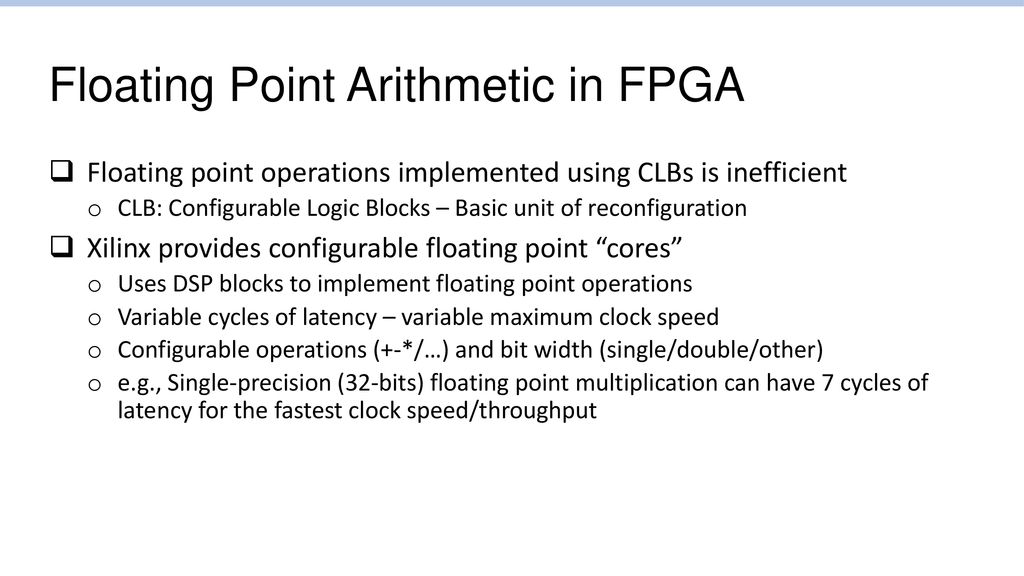

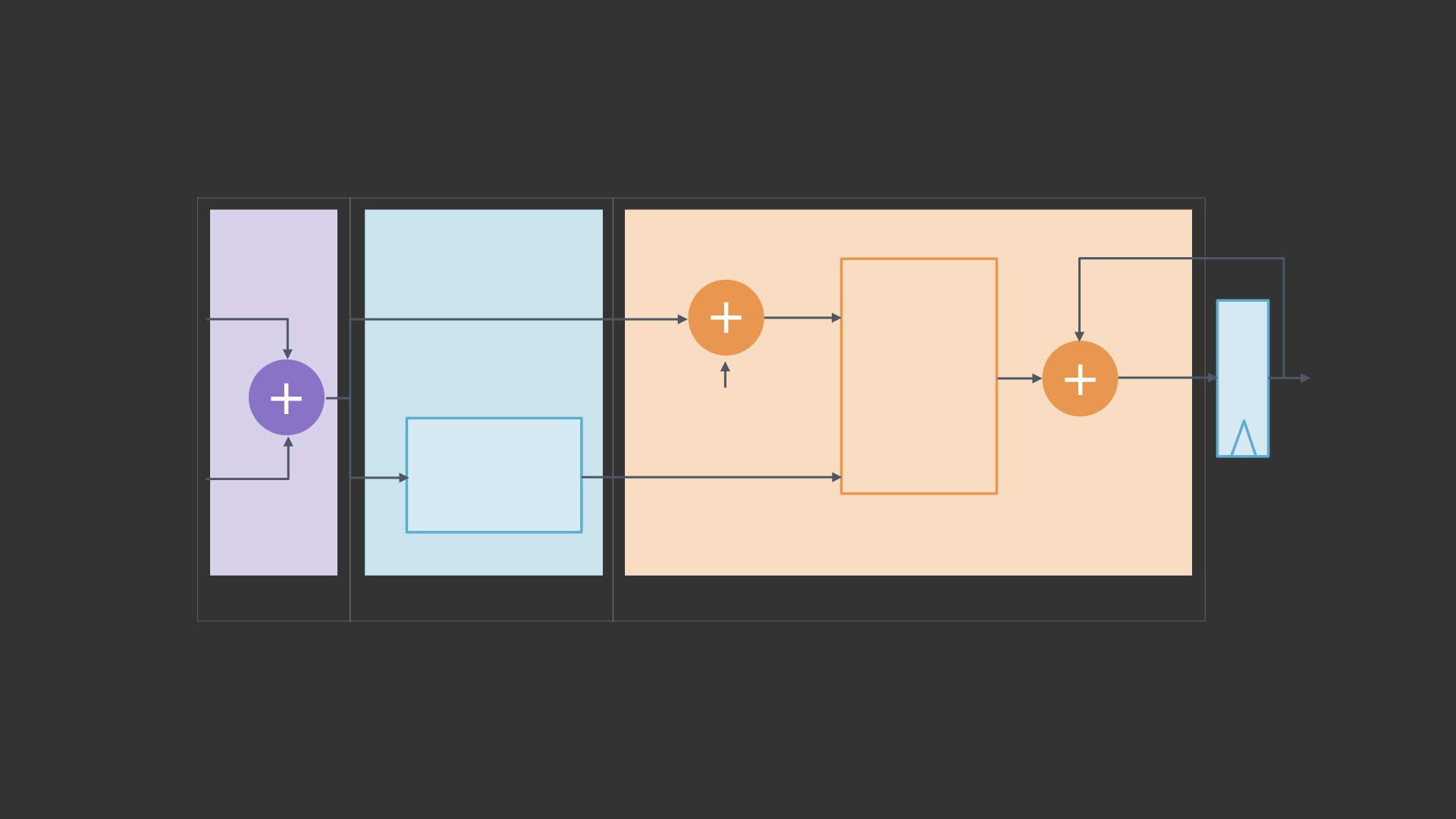

Floating-Point Advancements on Xilinx FPGAs: Bit Accuracy and Custom Precision — Xilinx Technical Article | ChipEstimate.com

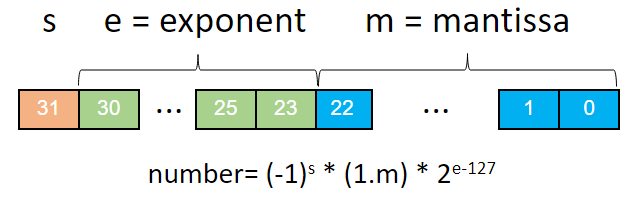

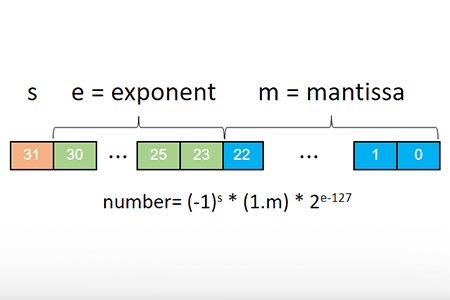

Design of FPGA based 32-bit Floating Point Arithmetic Unit and verification of its VHDL code using MATLAB

![PDF] FPGA implementation of an exact dot product and its application in variable-precision floating-point arithmetic by Yuanwu Lei, Yong Dou, Yazhuo Dong, Jie Zhou, Fei Xia · OA.mg · 10.1007/s11227-012-0860-0 PDF] FPGA implementation of an exact dot product and its application in variable-precision floating-point arithmetic by Yuanwu Lei, Yong Dou, Yazhuo Dong, Jie Zhou, Fei Xia · OA.mg · 10.1007/s11227-012-0860-0](https://og.oa.mg/FPGA%20implementation%20of%20an%20exact%20dot%20product%20and%20its%20application%20in%20variable-precision%20floating-point%20arithmetic.png?author=%20Yuanwu%20Lei,%20Yong%20Dou,%20Yazhuo%20Dong,%20Jie%20Zhou,%20Fei%20Xia)