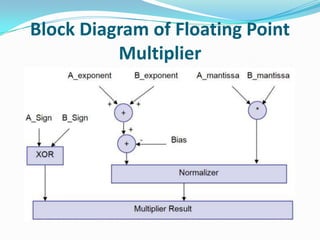

Figure 1 from Combined Integer and Floating Point Multiplication Architecture(CIFM) for FPGAs and Its Reversible Logic Implementation | Semantic Scholar

![PDF] An IEEE 754 double-precision floating-point multiplier for denormalized and normalized floating-point numbers | Semantic Scholar PDF] An IEEE 754 double-precision floating-point multiplier for denormalized and normalized floating-point numbers | Semantic Scholar](https://d3i71xaburhd42.cloudfront.net/22a7d96d78d26f7c400cf4c5f9e97f1ffe61200c/2-Figure2-1.png)

PDF] An IEEE 754 double-precision floating-point multiplier for denormalized and normalized floating-point numbers | Semantic Scholar

A low‐cost compensated approximate multiplier for Bfloat16 data processing on convolutional neural network inference

GitHub - avirlrma/Floating-Point-Multiplier-32-bit: A VHDL Team Project to multiply 32 Bit Floating Point Numbers.

Single Precision Floating Point Multiplier: Vinoth Kumar, B, Vijeyakumar, K N, Saranya, K: 9783960671558: Amazon.com: Books

An FPGA Based High Speed IEEE - 754 Double Precision Floating Point Adder/Subtractor and Multiplier Using Verilog

An efficient floating point multiplier design for high speed applications using Karatsuba algorithm and Urdhva-Tiryagbhyam algor

IEEE 754 Floating Point Pipelined Multiplier with Karatsuba for Mitigations of Area and Power | SpringerLink